# UM0340 User manual

SuperH<sup>™</sup> (SH) 32-bit RISC series SH-4, ST40 system architecture, volume 2: bus interfaces

This manual describes the ST40 family system architecture. It is split into four volumes:

ST40 System Architecture - Volume 1 System - ADCS 7153464.

ST40 System Architecture - Volume 2 Bus Interfaces - ADCS 7181720.

ST40 System Architecture - Volume 3 Video Devices - ADCS 7225754.

ST40 System Architecture - Volume 4 I/O Devices - ADCS 7225754.

# Contents

Drafaca

|     | iuce   |                            | 14 |

|-----|--------|----------------------------|----|

| Loc | cal me | mory interface (LMI)       | 1  |

| 1.1 | Intro  | duction                    | 1  |

|     | 1.1.1  | Main memory organization   | 1  |

|     | 1.1.2  | SDRAM controller features  | 1  |

|     | 1.1.3  | SuperHyway port            | 2  |

| 1.2 | Super  | rHyway interface           | 2  |

|     | 1.2.1  | SuperHyway port            | 2  |

|     | 1.2.2  | Control block              | 3  |

|     | 1.2.3  | Reaction to packets        | 5  |

|     | 1.2.4  | Pipelining request queue   | 10 |

|     | 1.2.5  | Coherency                  | 10 |

|     | 1.2.6  | Standby mode               | 10 |

| 1.3 | SDRA   | AM interface               | 11 |

|     | 1.3.1  | Main memory configuration  | 11 |

|     | 1.3.2  | SDRAM interface pins       | 13 |

|     | 1.3.3  | SDRAM devices              | 14 |

|     | 1.3.4  | Initializing SDRAM devices | 21 |

|     | 1.3.5  | Operations                 | 24 |

|     | 1.3.6  | Refresh                    | 25 |

|     | 1.3.7  | Power management           | 26 |

|     |        |                            |    |

*STMicroelectronics*

SH-4, ST40 System Architecture, Volume 2: Bus Interfaces

iv

- 477 -

## PRELIMINARY DATA

|   |     | 1.3.8  | Caution when programming SDRAM's mode register                    | 28 |

|---|-----|--------|-------------------------------------------------------------------|----|

|   |     | 1.3.9  | Using registered DIMM                                             | 28 |

|   |     | 1.3.10 | Others                                                            | 29 |

|   | 1.4 | Regist | er description                                                    | 30 |

|   |     | 1.4.1  | Version control register (LMI.VCR)                                | 30 |

|   |     | 1.4.2  | Memory interface mode register (LMI.MIM)                          | 36 |

|   |     | 1.4.3  | SDRAM control register (LMI.SCR)                                  | 40 |

|   |     | 1.4.4  | SDRAM timing register (LMI.STR)                                   | 43 |

|   |     | 1.4.5  | SDRAM row attribute registers (LMI.SDRA[0:1])                     | 47 |

|   |     | 1.4.6  | SDRAM row mode registers (LMI.SDMR[0:1])                          | 49 |

|   | 1.5 | Refere | ences                                                             | 49 |

| 2 | Enh | anced  | l flash memory interface (EMI)                                    | 51 |

|   | 2.1 | Overv  | iew                                                               | 51 |

|   | 2.2 | Featu  | res                                                               | 51 |

|   | 2.3 | Addre  | ss map                                                            | 53 |

|   | 2.4 | Opera  | tion                                                              | 58 |

|   |     | 2.4.1  | Supported transactions                                            | 58 |

|   |     | 2.4.2  | Data organization                                                 | 59 |

|   |     | 2.4.3  | Clock reconfiguration for synchronous interfaces                  | 61 |

|   |     | 2.4.4  | Master/slave mode                                                 | 61 |

|   | 2.5 | Defau  | lt and reset configuration                                        | 65 |

|   |     | 2.5.1  | Default configuration for asynchronous boot<br>(EMI_MPX_BOOT = 0) | 65 |

|   |     | 2.5.2  | Default configuration for MPX boot<br>(EMI_MPX_BOOT = 1)          | 67 |

|   | 2.6 | Peripł | neral interface with synchronous flash memory                     | 7  |

|   |     | suppo  | rt                                                                | 68 |

|   |     | 2.6.1  | Overview                                                          | 68 |

|   |     | 2.6.2  | Synchronous burst flash support                                   | 70 |

|   |     | 2.6.3  | Operating mode                                                    | 72 |

|   |     | 2.6.4  | Burst interrupt and burst reiteration                             | 73 |

iv

STMicroelectronics SH-4, ST40 System Architecture, Volume 2: Bus Interfaces

### PRELIMINARY DATA

|     | 2.6.5  | Synchronous burst enable                               | 75    |

|-----|--------|--------------------------------------------------------|-------|

|     | 2.6.6  | Support for lower clock rates                          | 75    |

|     | 2.6.7  | Initialization sequence                                | 76    |

|     | 2.6.8  | Flash subdecoding                                      | 76    |

|     | 2.6.9  | MEM_WAIT                                               | 77    |

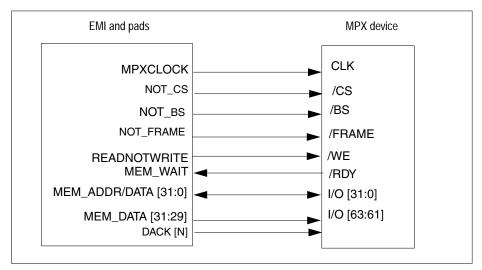

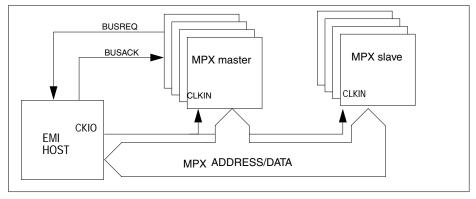

| 2.7 | MPX i  | interface                                              | 79    |

|     | 2.7.1  | MPX connection                                         | 80    |

|     | 2.7.2  | Endianness in MPX                                      | 81    |

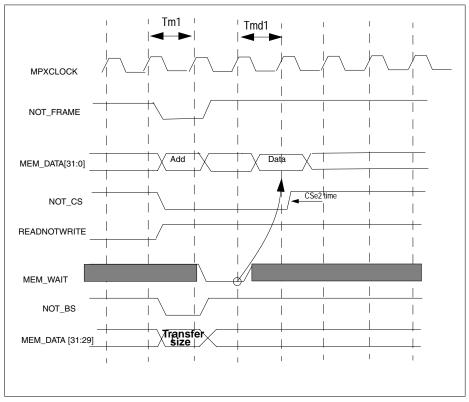

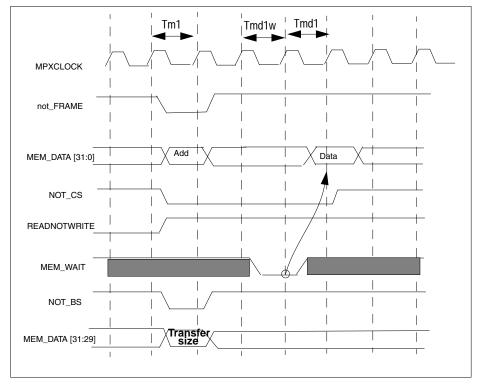

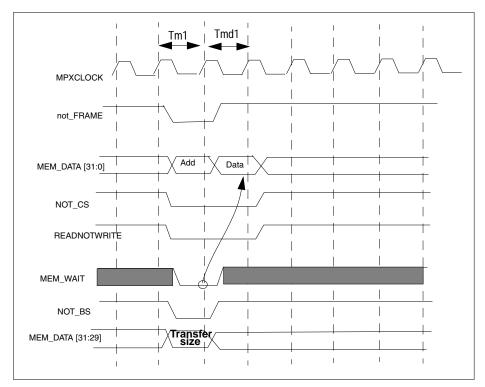

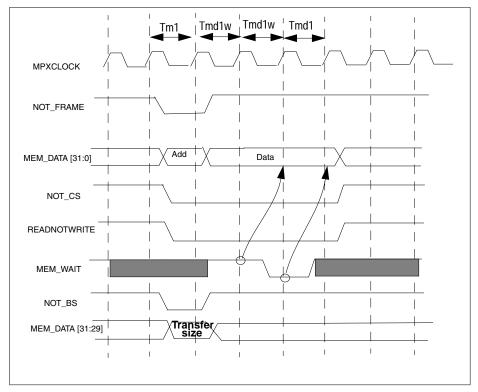

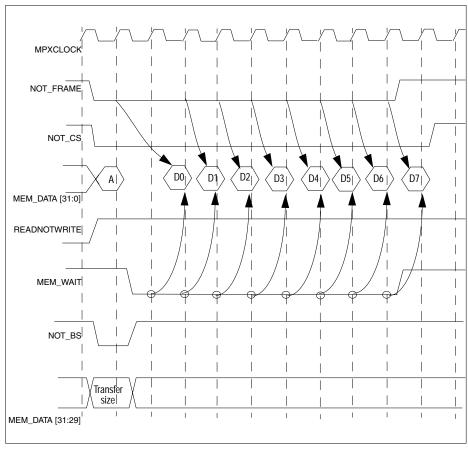

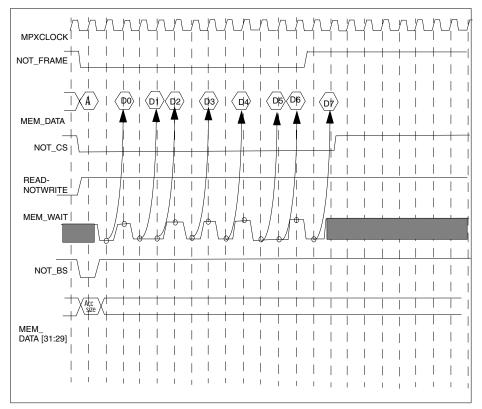

|     | 2.7.3  | External and internal wait states insertion            | 82    |

|     | 2.7.4  | MPX clock                                              | 82    |

|     | 2.7.5  | MPX interface timings                                  | 84    |

| 2.8 | SDRA   | M interface                                            | 92    |

|     | 2.8.1  | Typical access                                         | 92    |

|     | 2.8.2  | Description of signals                                 | 94    |

|     | 2.8.3  | SDRAM controller states                                | 97    |

|     | 2.8.4  | Supported SDRAM commands                               | 98    |

|     | 2.8.5  | Supported operations applicable to a single bank of 98 | SDRAM |

|     | 2.8.6  | Multiple banks                                         | 101   |

|     | 2.8.7  | Burst access behavior                                  | 103   |

|     | 2.8.8  | SDRAM accesses example                                 | 104   |

|     | 2.8.9  | SDRAM bank subdecoding and address selection           | 114   |

|     | 2.8.10 | SDRAM refresh cycle                                    | 117   |

|     | 2.8.11 | Power-down                                             | 119   |

|     | 2.8.12 | Initialization                                         | 121   |

| 2.9 | Regist | er definition                                          | 123   |

|     | 2.9.1  | EMI.STATUSCFG                                          | 123   |

|     | 2.9.2  | EMI.STATUSLOCK                                         | 124   |

|     | 2.9.3  | EMI.LOCK                                               | 125   |

|     | 2.9.4  | EMI.GENCFG                                             | 126   |

|     | 2.9.5  | EMI.SDRAMNOPGEN                                        | 127   |

|     | 2.9.6  | EMI.SDRAMMODEREG                                       | 128   |

|     | 2.9.7  | EMI.SDRAMINIT                                          | 129   |

STMicroelectronics

SH-4, ST40 System Architecture, Volume 2: Bus Interfaces

- /7/ -

|   |     | 2.9.8   | EMI.REFRESHINIT                | 130 |

|---|-----|---------|--------------------------------|-----|

|   |     | 2.9.9   | EMI.FLASHCLKSEL                | 131 |

|   |     | 2.9.10  | EMI.SDRAMCLKSEL                | 132 |

|   |     | 2.9.11  | EMI.MPXCLKSEL                  | 133 |

|   |     | 2.9.12  | EMI.CLKENABLE                  | 134 |

|   |     | 2.9.13  | Configuration register formats | 135 |

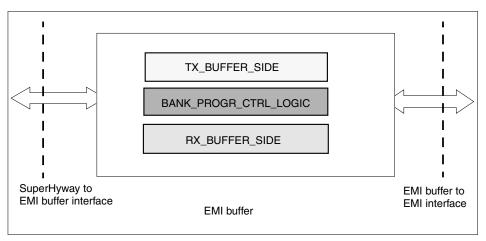

| 3 | EM  | l buffe | er                             | 151 |

|   | 3.1 | Overv   | riew                           | 151 |

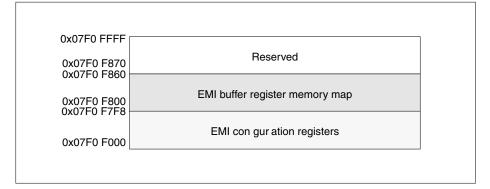

|   | 3.2 | Regist  | ter address map                | 153 |

|   |     | 3.2.1   | EMI memory map                 | 154 |

|   |     | 3.2.2   | Register descriptions          | 154 |

| 4 | PCI | bus i   | nterface (PCI)                 | 159 |

|   | 4.1 | Introd  | luction                        | 159 |

|   |     | 4.1.1   | Features                       | 160 |

|   |     | 4.1.2   | Supported PCI commands         | 161 |

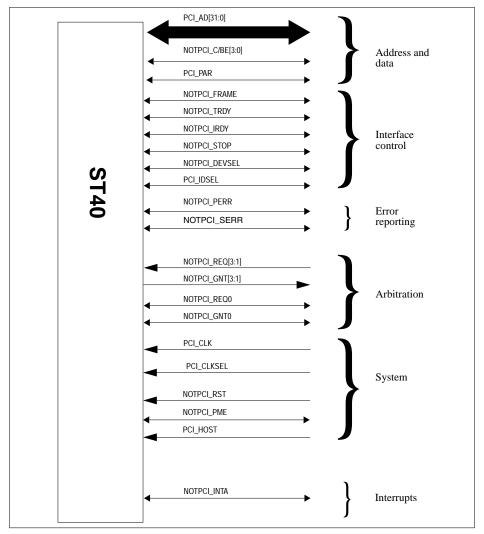

|   |     | 4.1.3   | Signal description             | 162 |

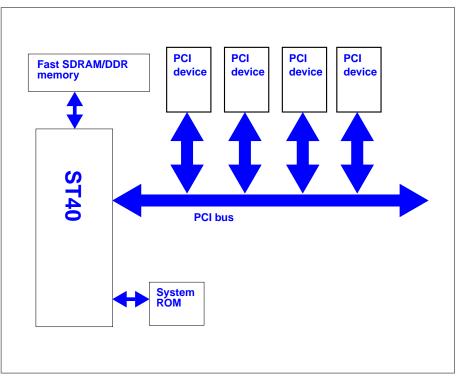

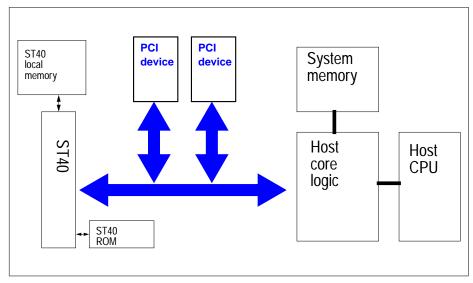

|   |     | 4.1.4   | Example configurations         | 163 |

|   |     | 4.1.5   | Basic operation                | 165 |

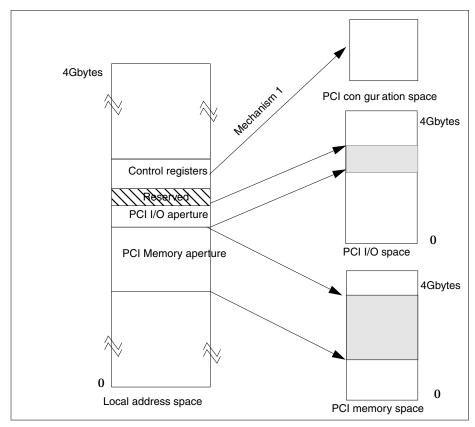

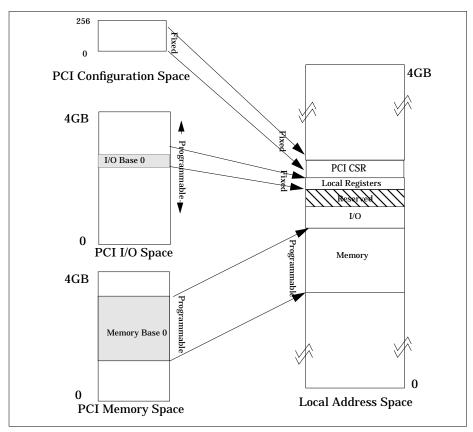

|   | 4.2 | Local   | address map                    | 165 |

|   | 4.3 | Trans   | actions                        | 166 |

|   |     | 4.3.1   | PCI master transactions        | 166 |

|   |     | 4.3.2   | PCI target transactions        | 171 |

|   |     | 4.3.3   | PCI errors                     | 176 |

|   | 4.4 | Opera   | tion                           | 178 |

|   |     | 4.4.1   | Operation mode                 | 178 |

|   |     | 4.4.2   | PCI bus arbitration            | 179 |

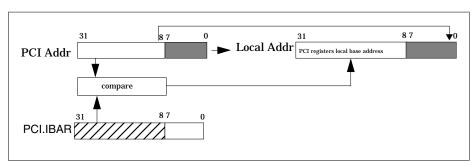

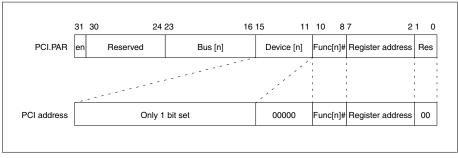

|   |     | 4.4.3   | Configuration access           | 180 |

|   |     | 4.4.4   | PCI interrupts                 | 181 |

## PRELIMINARY DATA

|   |     | 4.4.5          | Reset                                                      | 181        |

|---|-----|----------------|------------------------------------------------------------|------------|

|   |     | 4.4.6          | Clocking                                                   | 182        |

|   |     | 4.4.7          | Power management                                           | 183        |

|   |     | 4.4.8          | Endian issues                                              | 183        |

|   | 4.5 | Regist         | ters                                                       | 184        |

|   |     | 4.5.1          | Local register bank overview                               | 185        |

|   |     | 4.5.2          | Local configuration register bank overview                 | 187        |

|   |     | 4.5.3          | Configuration space register (CSR) bank overview           | 190        |

|   |     | 4.5.4          | Local register bank                                        | 192        |

|   |     | 4.5.5          | PCI access to wrapper                                      | 237        |

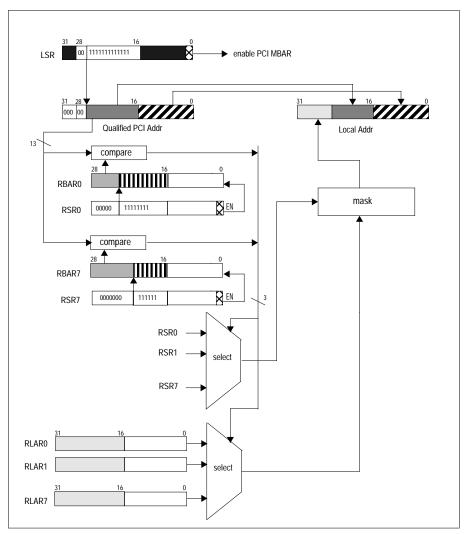

|   |     | 4.5.6          | Enhanced memory region mapping                             | 239        |

|   |     | 4.5.7          | CSR register bank                                          | 245        |

|   | 4.6 | Pin lis        | st                                                         | 278        |

|   | 4.7 | Refere         | ences                                                      | 280        |

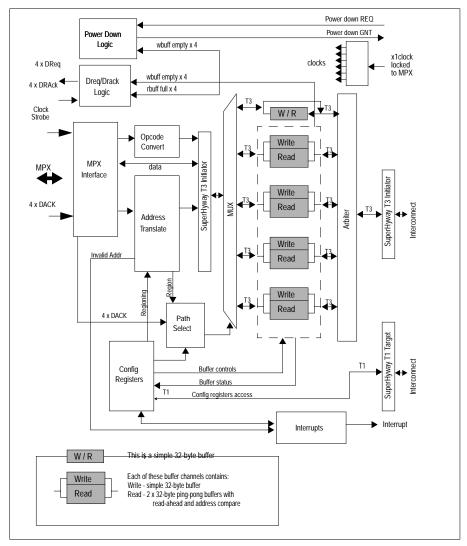

| 5 | Ext | ernal          | microprocessor interface (EMPI)                            | 281        |

|   | 5.1 | Overv          | iew                                                        | 281        |

|   | 5.2 | Featu          | res                                                        | 282        |

|   | 5.3 | Regist         | ter address map                                            | 283        |

|   | 5.4 | Opera          | tion                                                       | 288        |

|   |     | 5.4.1          | MPX interface                                              | 289        |

|   |     | 5.4.2          | Address translation                                        | 289        |

|   |     | 5.4.3          | Data buffer channels                                       | 289        |

|   |     | 5.4.4          | Association between buffer channels and external I signals | OMA<br>290 |

|   |     | 5.4.5          | Association between buffer channels and address re<br>291  | egions     |

|   |     |                | Opcode convert                                             | 293        |

|   |     | 5.4.6          | Opcode convert                                             | 293        |

|   |     | 5.4.6<br>5.4.7 | Arbiter                                                    | 293<br>293 |

|   |     |                | -                                                          |            |

|   |     | 5.4.7          | Arbiter                                                    | 293        |

SH-4, ST40 System Architecture, Volume 2: Bus Interfaces

- /7/ -

|   | 5.5 | Regis  | ter definition                                    | 294 |

|---|-----|--------|---------------------------------------------------|-----|

|   |     | 5.5.1  | EMPI.VCR_STATUS                                   | 294 |

|   |     | 5.5.2  | EMPI.VCR_VERSION                                  | 296 |

|   |     | 5.5.3  | EMPI.SYSTEM                                       | 297 |

|   |     | 5.5.4  | Interrupts                                        | 298 |

|   |     | 5.5.5  | MPX bus configuration                             | 300 |

|   |     | 5.5.6  | DMA channel controls                              | 302 |

|   |     | 5.5.7  | Address translation and buffer channel assignment | 307 |

| 6 | MP  | X arbi | iter (MPXARB)                                     | 315 |

|   | 6.1 | Overv  | riew                                              | 315 |

|   |     | 6.1.1  | Arbitration priority                              | 315 |

|   |     | 6.1.2  | Bus grant parking                                 | 316 |

|   |     | 6.1.3  | External request blocking                         | 316 |

|   |     | 6.1.4  | Options for external arbitration                  | 316 |

|   | 6.2 | Addre  | ess map                                           | 317 |

|   | 6.3 | Regis  | ter definition                                    | 318 |

|   |     | 6.3.1  | MPXARB.VCR                                        | 318 |

|   |     | 6.3.2  | MPXARB.CONTROL                                    | 319 |

|   |     | 6.3.3  | MPXARB.DLLCONTROL                                 | 323 |

|   |     | 6.3.4  | MPXARB.DLLSTATUS                                  | 323 |

|   | Арр | endic  | es                                                |     |

| A | Register address list |     |  |

|---|-----------------------|-----|--|

|   | Index                 | 339 |  |

# **Preface**

This document is part of the SuperH Documentation suite detailed below. Comments on this or other manuals in the SuperH Documentation Suite should be made by contacting your local STMicroelectronics Limited Sales Office or distributor.

# **Document identification and control**

Each book carries a unique identifier in the form:

ADCS nnnnnnx

**Where**, nnnnnn is the document number and x is the revision.

Whenever making comments on a document the complete identification ADCS nnnnnnx should be quoted.

# **ST40 documentation suite**

The ST40 documentation suite comprises the following volumes:

# ST40 Micro Toolset User's Guide

ADCS 7379953. This manual provides an introduction to the ST40 Micro Toolset and instructions for getting a simple OS21 application run on an STMicroelectronics' MediaRef platform. It also describes how to boot OS21 applications from ROM and how to port applications which use STMicroelectronics' STLite/OS20 operating systems to OS21.

- 77 –

STMicroelectronics

# **OS21 User's Manual**

ADCS 7358306. This manual describes the generic use of OS21 across supported platforms. It describes all the core features of OS21 and their use and details the OS21 function definitions. It also explains how OS21 differs to STLite/OS20, the API targeted at ST20.

# **OS21 for ST40 User Manual**

*ADCS 7358673.* This manual describes the use of OS21 on ST40 platforms. It describes how specific ST40 facilities are exploited by the OS21 API. It also describes the OS21 board support packages for ST40 platforms.

# 32-Bit RISC Series, SH-4 CPU Core Architecture

*ADCS 7182230.* This manual describes the architecture and instruction set of the SH4-1xx (previously known a ST40-C200) core as used by STMicroelectronics.

# 32-Bit RISC Series, SH-4, ST40 System Architecture

This manual describes the ST40 family system architecture. It is split into four volumes:

ST40 System Architecture - Volume 1 System - ADCS 7153464.

ST40 System Architecture - Volume 2 Bus Interfaces - ADCS 7171720.

ST40 System Architecture - Volume 3 Video Devices - ADCS 7225754.

ST40 System Architecture - Volume 4 I/O Devices - ADCS 7225754.

# **Conventions used in this guide**

# **General notation**

The notation in this document uses the following conventions:

- Sample code, keyboard input and file names,

- Variables and code variables,

- Equations and math,

- Screens, windows and dialog boxes,

- Instructions.

# **Hardware notation**

The following conventions are used for hardware notation:

- REGISTER NAMES and FIELD NAMES,

- PIN NAMES and SIGNAL NAMES.

# **Software notation**

Syntax definitions are presented in a modified Backus-Naur Form (BNF). Briefly:

- 1 Terminal strings of the language, that is those not built up by rules of the language, are printed in teletype font. For example, void.

- 2 Nonterminal strings of the language, that is those built up by rules of the language, are printed in italic teletype font. For example, *name*.

- 3 If a nonterminal string of the language starts with a nonitalicized part, it is equivalent to the same nonterminal string without that nonitalicized part. For example, vspace-name.

- 4 Each phrase definition is built up using a double colon and an equals sign to separate the two sides.

- 5 Alternatives are separated by vertical bars ('|').

- 6 Optional sequences are enclosed in square brackets ('[' and ']').

- 7 Items which may be repeated appear in braces ('{' and '}').

- 477 -

# Local memory interface (LMI)

# 1

# **1.1 Introduction**

The local memory interface (LMI) provides the interface between the ST40, the SuperHyway and the external main memory subsystem. It comprises a SuperHyway port and an SDRAM controller. The following descriptions highlight the key features of the main memory array, SDRAM controller and SuperHyway Port.

# 1.1.1 Main memory organization

- The array is organized as rows.

- Each row consists of one or more discrete devices or DIMM (single or double sided) modules arranged in sockets on a PCB.

# 1.1.2 SDRAM controller features

SDRAM controller comprises:

- programmable external bus width: 16-, 32- and 64-bit,

- dual or quad bank SDRAM, specifically the PC-SDRAM standard, or Double Data Rate (DDR) SDRAM (types cannot be mixed in the same system),

- main memory size: from 2 Mbytes to 2 Gbytes,

- memory modules supported: two rows of discrete SDRAM, single and double density DIMMs,

- SDRAM technology: 16-, 64-, 128- and 256-Mbit,

- SDRAM speed: 66, 100 and 133 MHz.

*STMicroelectronics*

- 57 –

# 1.1.3 SuperHyway port

The SuperHyway port includes:

- two 4-deep-in-order queue for requests and responses, respectively: supports pipelining of up to eight outstanding transactions on the SuperHyway,

- one control block (16-Mbyte space), containing the LMI module's VCR and SDRAM control registers

- 127 data blocks (16 Mbytes each) with access routed to the external memory.

# 1.2 SuperHyway interface

The functionality of the SuperHyway interface is described in the following subsections.

# 1.2.1 SuperHyway port

The SuperHyway port is divided into one control block and [n] number of data blocks. Each block is 16 Mbytes in size. The address range of the LMI is defined by VCR.BOT\_MB and VCR.TOP\_MB. Data blocks populate from VCR.BOT\_MB up to VCR.TOP\_MB (exclusive). The control block is assigned to 16 Mbytes, starting from VCR.TOP\_MB (inclusive). The control block contains the LMI module's VCR and SDRAM control registers.

|                 | LMI control block | LMI data blocks |

|-----------------|-------------------|-----------------|

| Port name       | LMI_CB            | LMI_DB          |

| Lowest address  | 0x0F00 0000       | 0x0800 0000     |

| Highest address | 0x0FFF FFFF       | 0x0EFF FFFF     |

#### Table 1: LMI address space

*Note:* In the ST40 implementation, VCR.BOT\_MB = 0x08 and VCR.TOP\_MB = 0x0F. Therefore data blocks populate the address range from 0x0800 0000 to 0x0EFF FFFF. This is summarized in Table 1

- 477 -

When the LMI is active, memory accesses from the SuperHyway to the data blocks cause accesses to be made on the external memory bus. Each external memory access consists of a number of phases, each one representing a specific action performed on the external memory bus. The behavior of the external pins of the LMI can be programmed to allow the LMI to drive the external memory bus in an appropriate way for different DDR SDRAM and SDRAM parts.

# 1.2.2 Control block

12 registers (64 bits each) are populated in the control block. Except VCR, each register contains no more than 32 defined bits. The following table summarizes all registers implemented in ST40's LMI module.

Address **Register name** Description Туре offset from Access size 0x0F00 0000 LMLVCR 32 or 64 Version control register, RW 0x00 0000 see Table 11 on page 30 LMI.MIM Memory interface mode. RW 0x00 0008 32 or 64 see Table 14 on page 36 0x00 0010 32 or 64 LMLSCR SDRAM control. see RW Table 15 on page 40 LMLSTR SDRAM timing, see RW 0x00 0018 32 or 64 Table 16 on page 43 LMLPBS Pin buffer strength, see 0x00 0020 datasheet LMLCOC Clock and pad control, RW 0x00 0028 32 or 64 see datasheet LMI.SDRA[0:1] SDRAM row attribute. RW 0x00 0030 to 32 or 64 0x00 0038 see Table 17 on page 47

*Note:* VCR.TOP\_MB *is 8-bit. Base Address = 0x*(VCR.TOP\_MB)000000.

Table 2: Control block registers

| ( |   |

|---|---|

|   | _ |

|   |   |

| Register name | Description                                                                                                | Туре | Address<br>offset from<br>0x0F00 0000 | Access size |

|---------------|------------------------------------------------------------------------------------------------------------|------|---------------------------------------|-------------|

| LMI.CIC       | Clock and pad status, see datasheet                                                                        | RO   | 0x00 0040                             | 32 or 64    |

| Reserved      | 0x00 0042 to<br>0x00 0080                                                                                  |      |                                       |             |

| LMI.SDMR[0:1] | SDRAM mode register,<br>see Section 1.4.6:<br>SDRAM row mode<br>registers<br>(LMI.SDMR[0:1]) on<br>page 49 | WO   | 0x8x xxxx<br>0x9x xxxx                | 32 or 64    |

| Unde ned      | Remaining                                                                                                  |      |                                       |             |

#### Table 2: Control block registers

*Note:* If the LMI is active, the transactions to the control block are processed only when there are no outstanding data block transactions. While the LMI is processing control block transactions, the SDRAMs are in idle state. After processing control block transactions, the LMI's DRAM controller then continues with its normal behavior which reflects the state of the control registers. The LMI ensures that the change from the original behavior to the subsequent behavior is achieved instantaneously at a boundary between SDRAM commands during the processing of that transaction.

# 1.2.3 Reaction to packets

The LMI does not initiate request packets to the SuperHyway. The LMI processes the following packets received from SuperHyway.

For accessing the control block:

- load 1/2/4/8-byte,<sup>1</sup>

- store 1/2/4/8-byte.<sup>1</sup>

For accessing the data block:

- load 1/2/4/8-byte,<sup>1</sup>

- load 16-byte (burst),<sup>2</sup>

- load 32-byte (burst),

- store1/2/4/8-byte,<sup>1</sup>

- store 16-byte (burst),<sup>3</sup>

- store 32-byte (burst),

- SWAP 4/8-byte,<sup>3</sup>

- Read-Modify-Write 4/8-byte.<sup>4</sup>

When accessing the control block, the LMI observes the rules below.

- LMI treats Load 1/2/4-byte and Store 1/2/4-byte as Load 8-byte and Store 8-byte. LMI performs read/write bytes according to eight byte-enable (or byte-mask) signals from the SuperHyway interface, regardless of Load1/2/4/ 8-byte and Store 1/2/4/8-byte. It is the responsibility of the SuperHyway initiator to assert correct byte-enable bits to ensure consistency with the intention of Load 1/2/4/8-byte and Store 1/2/4/8-byte.

- 2. LMI expects and performs wrap-around within a 32-byte range for Store32-byte and Load32-byte, respectively. In case of Load and Store 16-byte, LMI expects they are all 16-byte aligned. LMI raises the error flag in VCR when it detects a non-aligned load/store16 SuperHyway packet

- 3. LMI treats both SWAP 4-byte and SWAP 8-byte as SWAP 8-byte. It is the responsibility of the SuperHyway initiator to assert correct byte-enable bits to ensure the consistency with the intention of SWAP 4-byte and SWAP 8-byte.

- 17 -

5

STMicroelectronics

- Reads from the reserved control registers return 0. Writes to the reserved control registers are ignored.

- Reads from an undefined control register return an undefined value. Writes to undefined control registers are ignored.

- Accesses to the LMI's undefined control registers result in an error bit being set to indicate an access to a bad address. The full behavior of the transactions serviced by the LMI's control block is shown in *Table 3*.

| Packet received   | Condition                                                                                          | Effect                                                                                         |

|-------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Load 1/2/4/8-byte | Request is a subword (less than 8-byte)<br>or whole word load from an unde ned<br>control register | VCR.PERR.BAD_ADDR set<br>VCR.PERR.ERR_SNT set<br>Access ignored, error response<br>packet sent |

|                   | Request is a subword or whole word load from a reserved control register                           | An ordinary response sent<br>Return data all zeros                                             |

|                   | Request is a subword or whole-word load from an de ned control register                            | An ordinary response sent<br>Return data determined by control<br>register accessed            |

Table 3: Packets directed to LMI's control block

- 57

<sup>4.</sup> For supporting Read-Modify-Write, LMI receives a LOCK signal from the SuperHyway. LMI treats Read-Modify-Write as Load 8-byte and Store 8-byte when LOCK = 1 and LOCK = 0, respectively. LMI performs read or write bytes according to eight byte-enable (or byte-mask) signals from the SuperHyway interface. LMI treats both Read-Modify-Write 4-byte and Read-Modify-Write 8-byte as Read-Modify-Write 8-byte. It is the responsibility of the SuperHyway initiator to assert correct byte-enable bits to ensure the consistency with the intention of SWAP 4-byte and SWAP 8-byte.

| Packet received    | Condition                                                                | Effect                                                                                |

|--------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Store 1/2/4/8-byte | Request is a subword or whole-word store to an unde ned control register | VCR.PERR.BAD_ADDR set<br>VCR.PERR.ERR_SNT set                                         |

|                    |                                                                          | Access ignored, error response packet sent                                            |

|                    | Request is a subword or whole-word store to a reserved control register  | An ordinary response sent<br>Access ignored                                           |

|                    | Request is a subword or whole-word store to a de ned control register    | An ordinary response sent.<br>Written data determined by control<br>register accessed |

| All other packets  | Request is to an unde ned control register                               | VCR.PERR.BAD_OPC set<br>VCR.PERR.BAD_ADDR set.<br>VCR.PERR.ERR_SNT set                |

|                    |                                                                          | Access ignored, error response packet sent                                            |

|                    | Request is to a reserved or de ned control register                      | VCR.PERR.BAD_OPC set<br>VCR.PERR.ERR_SNT set.                                         |

|                    |                                                                          | Access ignored, error response packet sent                                            |

Table 3: Packets directed to LMI's control block

- /7/ -

When the data block is addressed, the LMI observes the rules below.

- The LMI does not service any packet directed to the data block when the SDRAM controller is disabled (MIM.DCE = 0).

- An out-of-range address is defined as a location beyond the address defined in the SDRAM row attribute register, see *Section 1.4.5: SDRAM row attribute registers (LMI.SDRA[0:1]) on page 47* for details. Reads from an out-of-range address return an undefined value. Writes to an out-of-range address are ignored. In either cases, the LMI responds with an error packet and set error flags in the VCR.The full behavior of the transactions serviced by the LMI's data block is shown in *Table 4*.

| Packet received                                         | Condition                                           | Effect                                                                                                                                                               |

|---------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Load 1-, 2-, 4- and<br>8-byte,                          | DRAM controller disabled                            | VCR.MERR.ERR_SNT set<br>VCR.MERR.DRAM_INACTIVE set                                                                                                                   |

| Load 32-byte,<br>Store 1-, 2-, 4-, and                  |                                                     | Access ignored, error response packet sent                                                                                                                           |

| 8-byte,<br>Store 32-byte,<br>SWAP,<br>Read-Modify-Write | DRAM controller enabled<br>Address within the range | An external memory access made<br>An ordinary response sent<br>Effect of external memory accesses and<br>any returned data depends on the<br>external implementation |

|                                                         | DRAM controller enabled<br>Address out of the range | VCR.MERR.ERR_SNT set<br>VCR.MERR.BAD_ADDR set<br>Access ignored, error response packet<br>sent                                                                       |

Table 4: Behavior of the transactions serviced by the LMI's data block

| Packet received               | Condition                                                             | Effect                                                                                                |

|-------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Load16-byte,<br>Store 16-byte | DRAM controller disabled                                              | VCR.MERR.ERR_SNT set<br>VCR.MERR.DRAM_INACTIVE set                                                    |

|                               |                                                                       | Access ignored, error response packet sent                                                            |

|                               | DRAM controller enabled                                               | External memory access made                                                                           |

|                               | Address within the range                                              | Ordinary response sent                                                                                |

|                               |                                                                       | Effect of external memory accesses and<br>any returned data depends on the<br>external implementation |

|                               | DRAM controller enabled Address<br>out of the range or not aligned at | VCR.MERR.ERR_SNT set<br>VCR.MERR.BAD_ADDR set                                                         |

|                               | 16-byte boundary                                                      | Access ignored, error response packet sent                                                            |

| All other packets             | DRAM controller disabled                                              | VCR.MERR.ERR_SNT set<br>VCR.MERR.DRAM_INACTIVE set                                                    |

|                               |                                                                       | Access ignored, error response packet sent                                                            |

|                               | DRAM controller enabled                                               | VCR.MERR.BAD_OPC set<br>VCR.MERR.ERR_SNT set                                                          |

|                               |                                                                       | Access ignored, error response packet sent                                                            |

Table 4: Behavior of the transactions serviced by the LMI's data block

# 1.2.4 Pipelining request queue

The SuperHyway Port maintains two 4-deep-in-order queues, one for request and the other one for response. Each entry in these queues has a 32-byte data buffer and 32 byte-enable bits to accommodate the data to and from main memory. The request queue's entry is transferred to the response queue once it is serviced by the SDRAM controller. The response queue's entry is retired once it is output to the SuperHyway. Accesses to any given address are observed to occur in the order which they are received by the LMI. Any LMI requester will see responses in the same order as the requests. Byte-gathering for the subsequent write requests is not supported in the LMI. It is assumed that each bus initiator module on the SuperHyway performs byte-gathering itself.

# 1.2.5 Coherency

The memory of the LMI is coherent as viewed from the SuperHyway. All requests are processed sequentially on the LMI in the order of the receipt of those requests by LMI. However, the system can decouple the generation of response packets from the actual external memory bus accesses. For store transactions, the corresponding store response packets may not be returned to the initiator on the SuperHyway until the write operations are actually completed on the DRAM interface. Since the local system is the sole owner of the external main memory and all the requests to the same address are processed in order (as they are received from the SuperHyway interface) on the SDRAM interface, memory coherency is achieved.

A swap packet comes with store data. When processing a swap request, the LMI initiates a read transaction on the DRAM interface. Once the data is received by the SDRAM controller, a write command is issued.

# 1.2.6 Standby mode

- 57

# **Entering standby mode**

The power management module asserts a STBY\_REQ signal to the LMI module. From this point on, the LMI can not take new requests from the SuperHyway. The LMI continues to service all the transaction requests in the queue. Upon concluding the last request, the LMI issues a power-down command to the SDRAM, and asserts STBY\_ACK to the power management module. In return, the power management module stops providing clock to the LMI. Consequently, the LMI's MCLKO pin is stopped at high.

# Leaving standby mode

The power management module de-asserts STBY\_REQ and the LMI responds with de-assertion of STBY\_ACK. The power management module then restores the clock supply before it de-asserts STBY\_REQ and MCLKO starts toggling accordingly.

# 1.3 SDRAM interface

The LMI's SDRAM controller can be configured to support PC-SDRAM and DDR SDRAMs. The functionality of the SDRAM interface is described in the following subsections.

# 1.3.1 Main memory configuration

The main memory is organized in rows. The data bus width can be programmed to 16-bit, 32-bit or 64-bit by writing MIM's BW field, see *Section 1.4.2: Memory interface mode register (LMI.MIM) on page 36.* The population on each row ranges from 2 Mbytes to 2 Gbytes. The different rows may have different size or technology of SDRAM population, but must have the same data bus width, burst length and share the same timing parameters defined in the STR register. SDRAM devices on the same row must be the same kind (for example, 4Mx16, 2-bank). Either PC SDRAM or DDR SDRAM can be supported but they cannot be mixed in main memory.

Note: The term "row" is used in two places, that is, SDRAM device's internal "row" address and main memory subsystem's "row" array. In this chapter, "row" indicates subsystem's row, while "(internal) row" means SDRAM's row address.

The upper boundary address of each row is defined in the SDRA.UBA field (SDRAM row attribute register's upper bound address). The request address [31:21] is compared to SDRA.UBA [31:21] to determine which NOT\_CSA (chip selection) signal is to be asserted. A NOT\_CSA signal is applied to all SDRAM devices on the same row.

Memory locations in these two rows must be contiguous in physical address space. SDRA1.UBA must be larger or equal to SDRA0.UBA. If the system consists of only one row (or DIMM), then it needs to be placed in the area corresponding to CS0 and SDRA0.UBA = SDRA1.UBA must be programmed. CS0 is asserted if the SuperHyway request access to LMI's data block and the request address [31:21] is less than SDRA0.UBA (exclusive).

- 77 -

11

STMicroelectronics

SDRA0.UBA has the priority over SDRA1.UBA if they are equal. If the physical address is less than SDRA0.UBA, CS0 is asserted. If it is not less than SDRA0.UBA but is less than SDRA1.UBA, CS1 is asserted. Other cases are errors and are recorded in the VCR's error flag.

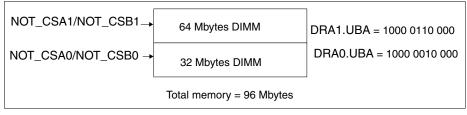

The following figure depicts a 64-bit wide, 96 Mbyte main memory subsystem. It is assumed VCR.BOT\_MB = 0x08.

Figure 1: Main memory configuration example

Memory configuration can be little endian or big endian. The LMI is independent of endianness when the external bus width is 64 bit. When the external bus width is 32-bit, memory interface register MIM.ENDIAN bit (read only) indicates the endianness of the system.

- 57

# 1.3.2 SDRAM interface pins

The external pins are described in *Table 5*.

| Name         | I/O    | Size | Description                                                                                                                                                                                                         |

|--------------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLKO        | Output | 1    | SDRAM clock out                                                                                                                                                                                                     |

|              |        |      | 66, 100 or 133 MHz clock output                                                                                                                                                                                     |

| NOT_MCLKO    | Output | 1    | MCLKO and NOT_MCLKO are differential clock outputs to DDR SDRAM.                                                                                                                                                    |

| CKE[1:0]     | Output | 2    | Clock enable                                                                                                                                                                                                        |

|              |        |      | Activates the clock signal when high and deactivates when low                                                                                                                                                       |

|              |        |      | By deactivating the clock, CKE low initiates the power-down mode, self-refresh mode or suspend mode.                                                                                                                |

| NOT_CSA[1:0] | Output | 2    | Chip select                                                                                                                                                                                                         |

| NOT_CSB[1:0] |        | 2    | Perform the function of selecting the particular SDRAM components during the active state <sup>A</sup>                                                                                                              |

| NOT_WEA      | Output | 1    | Write enable signal                                                                                                                                                                                                 |

| NOT_WEB      |        | 1    | WE asserted during writes to SDRAM                                                                                                                                                                                  |

| MA[14:0]     | Output | 15   | Row and column address                                                                                                                                                                                              |

| BA[1:0]      | Output | 2    | Bank address                                                                                                                                                                                                        |

| MD[63:0]     | I/O    | 64   | Memory data                                                                                                                                                                                                         |

| DQS[7:0]     | I/O    | 8    | Input/output data strobe                                                                                                                                                                                            |

|              |        |      | Used in DDR SDRAM only                                                                                                                                                                                              |

|              |        |      | These pins provide the read and write data strobe<br>signal to/from the receiver circuit of DRAM<br>controller. LMI drives DQS pins in write (Store)<br>cycles, while DDR SDRAM drives it in read (Load)<br>cycles. |

Table 5: SDRAM interface pins

- 177 -

| Name     | I/O    | Size | Description                                                                                                                        |

|----------|--------|------|------------------------------------------------------------------------------------------------------------------------------------|

| DQM[7:0] | Output | 8    | Input/output data mask                                                                                                             |

|          |        |      | For regular SDRAM, these pins act as synchronized<br>output enables during read cycles and as byte<br>enables during write cycles. |

|          |        |      | For DDR SDRAM, these pins act as byte enables during write cycles.                                                                 |

| NOT_RASA | Output | 1    | Row address strobe                                                                                                                 |

| NOT_RASB |        | 1    | The NOT_RASA and NOT_RASB are multiple copies of the same logic RAS signal used to generate encoded SDRAM command.                 |

| NOT_CASA | Output | 1    | Column address strobe                                                                                                              |

| NOT_CASB |        | 1    | The NOT_CASA and NOT_CASB are multiple copies of the same logic CAS signal used to generate encoded SDRAM command.                 |

| VREF     | Input  | 1    | Input reference voltage                                                                                                            |

#### Table 5: SDRAM interface pins

A. There are two copies of NOT\_CS for each physical memory row to reduce the loading.

To accommodate various loading conditions, the buffer strength of the pins is programmable. This feature can minimize unnecessary power consumption while still meeting the SDRAM device's timing requirements. See *Section 1.4.5* for details.

## 1.3.3 SDRAM devices

- 477 -

The LMI splits the physical memory address into banks, (internal) row and column addresses. The LMI contains 17 external address pins. BA[1:0] specifies which bank, while MA[14:0] indicates row and column addresses in each bank. The (internal) row address selects a page in an SDRAM. The column address selects a datum in a row. The LMI supports memories where row addresses are up to 15 bits.

The following three tables summarize various SDRAM devices which are used to construct the memory subsystem in three different data bus widths. They also illustrate MA pins mux-ing vs SDRAM address split. LMI's MA[14:0] pins are

STMicroelectronics SH-4, ST40 System Architecture, Volume 2: Bus Interfaces directly connected to SDRAM's A[14:0]. The address split column in the table specifies the row and column address split within a given bank.

Using the second entry as an example, 2 of 16 Mbytes (2Mx8 type, two banks) SDRAMs are used to construct a row of main memory. The SDRAM's internal row and column address bits are 11 and 9, respectively. The page size is 1 Kbyte. Total memory on this row is 4 Mbytes. The CPU's physical address PA [11] is output to BA[0] pins in both RAS and CAS phases. MA[10] is driven with PA [12] in RAS phase. AP (Auto Precharge) option is output to MA[10] in CAS phase, although the ST40 LMI does not issue either read-with auto-precharge or write-with auto-precharge commands.

# 16-bit data bus interface

| SDRAM<br>type      | Address<br>split | Page<br>size | Row<br>size  | RAS<br>CAS | BA1      | BA0      | MA12 | MA11     | MA10<br>/AP | MA9      | MA8     | MA<br>[7:0]      |

|--------------------|------------------|--------------|--------------|------------|----------|----------|------|----------|-------------|----------|---------|------------------|

| 16 Mbit<br>2 bank  |                  |              |              |            |          |          |      |          |             |          |         |                  |

| 1 Mbit<br>x 16     | 11 x 8           | 512<br>bytes | 2<br>Mbytes  | RAS<br>CAS |          | 11<br>11 |      |          | 12<br>AP    | 10       | 9       | [20:13]<br>[8:1] |

| 2 Mbit<br>x 8      | 11 x 9           | 1<br>Kbytes  | 4<br>Mbytes  | RAS<br>CAS |          | 11<br>11 |      |          | 12<br>AP    | 10       | 21<br>9 | [20:13]<br>[8:1] |

| 4 Mbit<br>x 4      | 11 x 10          | 2<br>Kbytes  | 8<br>Mbytes  | RAS<br>CAS |          | 11<br>11 |      |          | 12<br>AP    | 22<br>10 | 21<br>9 | [20:13]<br>[8:1] |

| 64 Mbit<br>2 bank  |                  |              |              |            |          |          |      |          |             |          |         |                  |

| 4 Mbit<br>x 16     | 13 x 8           | 512<br>bytes | 8<br>Mbytes  | RAS<br>CAS |          | 11<br>11 | 12   | 10       | 9<br>AP     | 22       | 21      | [20:13]<br>[8:1] |

| 8 Mbit<br>x 8      | 13 x 9           | 1<br>Kbytes  | 16<br>Mbytes | RAS<br>CAS |          | 11<br>11 | 12   | 10       | 23<br>AP    | 22       | 21<br>9 | [20:13]<br>[8:1] |

| 16 Mbit<br>x 4     | 13 x 10          | 2<br>Kbytes  | 32<br>Mbytes | RAS<br>CAS |          | 11<br>11 | 12   | 24       | 23<br>AP    | 22<br>10 | 21<br>9 | [20:13]<br>[8:1] |

| 64 Mbit<br>4 bank  |                  |              |              |            |          |          |      |          |             |          |         |                  |

| 4 Mbit<br>x 16     | 12 x 8           | 512<br>bytes | 8<br>Mbytes  | RAS<br>CAS | 12<br>12 | 11<br>11 |      | 10       | 9<br>AP     | 22       | 21      | [20:13]<br>[8:1] |

| 8 M bit<br>x 8     | 12 x 9           | 1<br>Kbyte   | 16<br>Mbytes | RAS<br>CAS | 12<br>12 | 11<br>11 |      | 10       | 23<br>AP    | 22       | 21<br>9 | [20:13]<br>[8:1] |

| 16 Mbit<br>x 4     | 12 x 10          | 2<br>Kbytes  | 32<br>Mbytes | RAS<br>CAS | 12<br>12 | 11<br>11 |      | 24       | 23<br>AP    | 22<br>10 | 21<br>9 | [20:13]<br>[8:1] |

| 128 Mbit<br>4 bank |                  |              |              |            |          |          |      |          |             |          |         |                  |

| 8 Mbit<br>x 16     | 12 x 9           | 1<br>Kbyte   | 16<br>Mbytes | RAS<br>CAS | 12<br>12 | 11<br>11 |      | 10       | 23<br>AP    | 22       | 21<br>9 | [20:13]<br>[8:1] |

| 16 Mbit<br>x 8     | 12 x 10          | 2<br>Kbytes  | 32<br>Mbytes | RAS<br>CAS | 12<br>12 | 11<br>11 |      | 24       | 23<br>AP    | 22<br>10 | 21<br>9 | [20:13]<br>[8:1] |

| 32 Mbit<br>x 4     | 12 x 11          | 4<br>Kbytes  | 64<br>Mbytes | RAS<br>CAS | 12<br>12 | 25<br>25 |      | 24<br>11 | 23<br>AP    | 22<br>10 | 21<br>9 | [20:13]<br>[8:1] |

Table 6: Row and column addressing for memory size and number of banks (32-bit interface)

| SDRAM<br>type      | Address<br>split | Page<br>size | Row<br>size   | RAS<br>CAS | BA1      | BA0      | MA12 | MA11     | MA10<br>/AP | MA9      | MA8     | MA<br>[7:0]      |

|--------------------|------------------|--------------|---------------|------------|----------|----------|------|----------|-------------|----------|---------|------------------|

| 256 Mbit<br>4 bank |                  |              |               |            |          |          |      |          |             |          |         |                  |

| 16 Mbit<br>x 16    | 13 x 9           | 1<br>Kbyte   | 32<br>Mbytes  | RAS<br>CAS | 12<br>12 | 11<br>11 | 10   | 24       | 23<br>AP    | 22       | 21<br>9 | [20:13]<br>[8:1] |

| 32 Mbit<br>x 8     | 13 x 10          | 2<br>Kbytes  | 64<br>Mbytes  | RAS<br>CAS | 12<br>12 | 11<br>11 | 25   | 24       | 23<br>AP    | 22<br>10 | 21<br>9 | [20:13]<br>[8:1] |

| 64 Mbit<br>x 4     | 13 x 11          | 4<br>Kbytes  | 128<br>Mbytes | RAS<br>CAS | 12<br>12 | 26<br>26 | 25   | 24<br>11 | 23<br>AP    | 22<br>10 | 21<br>9 | [20:13]<br>[8:1] |

Table 6: Row and column addressing for memory size and number of banks (32-bit interface)

# 32-bit data bus interface

| SDRAM<br>type         | Address<br>split | Page<br>size | Row<br>size  | RAS<br>CAS | BA1      | BA0      | MA12 | MA11 | MA10<br>/AP | MA9      | MA8       | MA<br>[7:0]      |

|-----------------------|------------------|--------------|--------------|------------|----------|----------|------|------|-------------|----------|-----------|------------------|

| 16 Mbit<br>2 bank     |                  |              |              |            |          |          |      |      |             |          |           |                  |

| 1Mbit<br>x 16         | 11 x 8           | 1<br>Kbytes  | 4<br>Mbytes  | RAS<br>CAS |          | 13<br>13 |      |      | 12<br>AP    | 11       | 10        | [21:14]<br>[9:2] |

| 2Mbits<br>x 8         | 11 x 9           | 2<br>Kbytes  | 8<br>Mbytes  | RAS<br>CAS |          | 13<br>13 |      |      | 12<br>AP    | 11       | 22<br>10  | [21:14]<br>[9:2] |

| 4Mbits<br>x 4         | 11 x 10          | 4<br>Kbytes  | 16<br>Mbytes | RAS<br>CAS |          | 13<br>13 |      |      | 12<br>AP    | 23<br>11 | 22<br>10  | [21:14]<br>[9:2] |

| 64Mbit<br>2 bank      |                  |              |              |            |          |          |      |      |             |          |           |                  |

| 4Mbits<br>x 16        | 13 x 8           | 1<br>Kbytes  | 16<br>Mbytes | RAS<br>CAS |          | 13<br>13 | 12   | 11   | 10<br>AP    | 23       | 22        | [21:14]<br>[9:2] |

| 8Mbits<br>x 8         | 13 x 9           | 2<br>Kbytes  | 32<br>Mbytes | RAS<br>CAS |          | 13<br>13 | 12   | 11   | 24<br>AP    | 23       | 22<br>10  | [21:14]<br>[9:2] |

| 16Mbits<br>x 4        | 13 x 10          | 4<br>Kbytes  | 64<br>Mbytes | RAS<br>CAS |          | 13<br>13 | 12   | 25   | 24<br>AP    | 23<br>11 | 22<br>10  | [21:14]<br>[9:2] |

| 64Mbit<br>4 bank      |                  |              |              |            |          |          |      |      |             |          |           |                  |

| 2Mbits<br>x 32        | 11 x 8           | 1<br>Kbytes  | 8<br>Mbytes  | RAS<br>CAS | 12<br>12 | 13<br>13 |      |      | 10<br>AP    | 11       | 22<br>AP* | [21:14]<br>[9:2] |

| 4Mbits<br>x 16        | 12 x 8           | 1<br>Kbytes  | 16<br>Mbytes | RAS<br>CAS | 12<br>12 | 13<br>13 |      | 11   | 10<br>AP    | 23       | 22        | [21:14]<br>[9:2] |

| 8Mbits<br>x 8         | 12 x 9           | 2<br>Kbytes  | 32<br>Mbytes | RAS<br>CAS | 12<br>12 | 13<br>13 |      | 11   | 24<br>AP    | 23       | 22<br>10  | [21:14]<br>[9:2] |

| 16Mbits<br>x 4        | 12 x 10          | 4<br>Kbytes  | 64<br>Mbytes | RAS<br>CAS | 12<br>12 | 13<br>13 |      | 25   | 24<br>AP    | 23<br>11 | 22<br>10  | [21:14]<br>[9:2] |

| 128<br>Mbit<br>4 bank |                  |              |              |            |          |          |      |      |             |          |           |                  |

| 8 Mbit<br>x 16        | 12 x 9           | 2<br>Kbytes  | 32<br>Mbytes | RAS<br>CAS | 12<br>12 | 13<br>13 |      | 11   | 24<br>AP    | 23       | 22<br>10  | [21:14]<br>[9:2] |

| 16 Mbit<br>x 8        | 12 x 10          | 4<br>Kbytes  | 64<br>Mbytes | RAS<br>CAS | 12<br>12 | 13<br>13 |      | 25   | 24<br>AP    | 23<br>11 | 22<br>10  | [21:14]<br>[9:2] |

Table 7: Row and column addressing for memory size and number of banks (32-bit interface)

| SDRAM<br>type         | Address<br>split | Page<br>size | Row<br>size | RAS<br>CAS | BA1 | BA0 | MA12 | MA11 | MA10<br>/AP | MA9 | MA8 | MA<br>[7:0] |

|-----------------------|------------------|--------------|-------------|------------|-----|-----|------|------|-------------|-----|-----|-------------|

| 32 Mbit               | 12 x 11          | 8            | 128         | RAS        | 26  | 13  |      | 25   | 24          | 23  | 22  | [21:14]     |

| x 4                   |                  | Kbytes       | Mbytes      | CAS        | 26  | 13  |      | 12   | AP          | 11  | 10  | [9:2]       |

| 256<br>Mbit<br>4 bank |                  |              |             |            |     |     |      |      |             |     |     |             |

| 16 Mbit               | 13 x 9           | 2            | 64          | RAS        | 12  | 13  | 11   | 25   | 24          | 23  | 22  | [21:14]     |

| x 16                  |                  | Kbytes       | Mbytes      | CAS        | 12  | 13  |      |      | AP          |     | 10  | [9:2]       |

| 32 Mbit               | 13 x 10          | 4            | 128         | RAS        | 12  | 13  | 26   | 25   | 24          | 23  | 22  | [21:14]     |

| x 8                   |                  | Kbytes       | Mbytes      | CAS        | 12  | 13  |      |      | AP          | 11  | 10  | [9:2]       |

| 64 Mbit               | 13 x 11          | 8            | 256         | RAS        | 27  | 13  | 26   | 25   | 24          | 23  | 22  | [21:14]     |

| x 4                   |                  | Kbytes       | Mbytes      | CAS        | 27  | 13  |      | 12   | AP          | 11  | 10  | [9:2]       |

Table 7: Row and column addressing for memory size and number of banks (32-bit interface)

# 64-bit data bus interface

| SDRAM<br>type      | Address<br>split | Page<br>size | Row<br>size   | RAS<br>CAS | BA<br>1  | BA0      | MA12 | MA11 | MA10<br>/AP | MA9      | MA8       | MA<br>[7:0]       |

|--------------------|------------------|--------------|---------------|------------|----------|----------|------|------|-------------|----------|-----------|-------------------|

| 16 Mbit<br>2 bank  |                  |              |               |            |          |          |      |      |             |          |           |                   |

| 1 Mbit<br>x 16     | 11 x 8           | 2<br>Kbytes  | 8<br>Mbytes   | RAS<br>CAS |          | 13<br>13 |      |      | 14<br>AP    | 12       | 11        | [22:15]<br>[10:3] |

| 2 Mbits<br>x 8     | 11 x 9           | 4<br>Kbytes  | 16<br>Mbytes  | RAS<br>CAS |          | 13<br>13 |      |      | 14<br>AP    | 12       | 23<br>11  | [22:15]<br>[10:3] |

| 4 Mbits<br>x 4     | 11 x 10          | 8<br>Kbytes  | 32<br>Mbytes  | RAS<br>CAS |          | 13<br>13 |      |      | 14<br>AP    | 24<br>12 | 23<br>11  | [22:15]<br>[10:3] |

| 64 Mbit<br>2 bank  |                  |              |               |            |          |          |      |      |             |          |           |                   |

| 4 Mbits<br>x 16    | 13 x 8           | 2<br>Kbytes  | 32<br>Mbytes  | RAS<br>CAS |          | 13<br>13 | 14   | 12   | 11<br>AP    | 24       | 23        | [22:15]<br>[10:3] |

| 8 Mbits<br>x 8     | 13 x 9           | 4<br>Kbytes  | 64<br>Mbytes  | RAS<br>CAS |          | 13<br>13 | 14   | 12   | 25<br>AP    | 24       | 23<br>11  | [22:15]<br>[10:3] |

| 16 Mbits<br>x 4    | 13 x 10          | 8<br>Kbytes  | 126<br>Mbytes | RAS<br>CAS |          | 13<br>13 | 14   | 26   | 25<br>AP    | 24<br>12 | 23<br>11  | [22:15]<br>[10:3] |

| 64 Mbit<br>4 bank  |                  |              |               |            |          |          |      |      |             |          |           |                   |

| 2 Mbits<br>x 32    | 11 x 8           | 2<br>Kbytes  | 16<br>Mbytes  | RAS<br>CAS | 14<br>14 | 13<br>13 |      |      | 11<br>AP    | 12       | 23<br>AP* | [22:15]<br>[10:3] |

| 4 Mbits<br>x 16    | 12 x 8           | 2<br>Kbytes  | 32<br>Mbytes  | RAS<br>CAS | 14<br>14 | 13<br>13 |      | 12   | 11<br>AP    | 24       | 23        | [22:15]<br>[10:3] |

| 8 Mbits<br>x 8     | 12 x 9           | 4<br>Kbytes  | 64<br>Mbytes  | RAS<br>CAS | 14<br>14 | 13<br>13 |      | 12   | 25<br>AP    | 24       | 23<br>11  | [22:15]<br>[10:3] |

| 16 Mbits<br>x 4    | 12x10            | 8K           | 128M          | RAS<br>CAS | 14<br>14 | 13<br>13 |      | 26   | 25<br>AP    | 24<br>12 | 23<br>11  | [22:15]<br>[10:3] |

| 128 Mbit<br>4 bank |                  |              |               |            |          |          |      |      |             |          |           |                   |

| 8 Mbit<br>x 16     | 12 x 9           | 4<br>Kbytes  | 64<br>Mbytes  | RAS<br>CAS | 14<br>14 | 13<br>13 |      | 12   | 25<br>AP    | 24       | 23<br>11  | [22:15]<br>[10:3] |

| 16 Mbit<br>x 8     | 12 x 10          | 8<br>Kbytes  | 128<br>Mbytes | RAS<br>CAS | 14<br>14 | 13<br>13 |      | 26   | 25<br>AP    | 24<br>12 | 23<br>11  | [22:15]<br>[10:3] |

Table 8: Row and column addressing for memory size and number of banks (64-bit interface)

- 57 -----

| SDRAM<br>type      | Address<br>split | Page<br>size | Row<br>size   | RAS<br>CAS | BA<br>1  | BA0      | MA12 | MA11     | MA10<br>/AP | MA9      | MA8      | MA<br>[7:0]       |

|--------------------|------------------|--------------|---------------|------------|----------|----------|------|----------|-------------|----------|----------|-------------------|

| 32 Mbit<br>x 4     | 12 x 11          | 16<br>Kbytes | 256<br>Mbytes | RAS<br>CAS | 14<br>14 | 27<br>27 |      | 26<br>13 | 25<br>AP    | 24<br>12 | 23<br>11 | [22:15]<br>[10:3] |

| 256 Mbit<br>4 bank |                  |              |               |            |          |          |      |          |             |          |          |                   |

| 16 Mbit<br>x 16    | 13 x 9           | 4<br>Kbytes  | 128<br>Mbytes | RAS<br>CAS | 14<br>14 | 13<br>13 | 12   | 26       | 25<br>AP    | 24       | 23<br>11 | [22:15]<br>[10:3] |

| 32 Mbit<br>x 8     | 13 x 10          | 8<br>Kbytes  | 256<br>Mbytes | RAS<br>CAS | 14<br>14 | 13<br>13 | 27   | 26       | 25<br>AP    | 24<br>12 | 23<br>11 | [22:15]<br>[10:3] |

| 64 Mbit<br>x 4     | 13 x 11          | 16<br>Kbytes | 512<br>Mbytes | RAS<br>CAS | 14<br>14 | 28<br>28 | 27   | 26<br>13 | 25<br>AP    | 24<br>12 | 23<br>11 | [22:15]<br>[10:3] |

Table 8: Row and column addressing for memory size and number of banks (64-bit interface)

*Note:* AP PIN: *LMI uses the* MIM.BY32AP *bit to determine if the* MA8 *pin is used to indicate the PRE and PALL commands.*

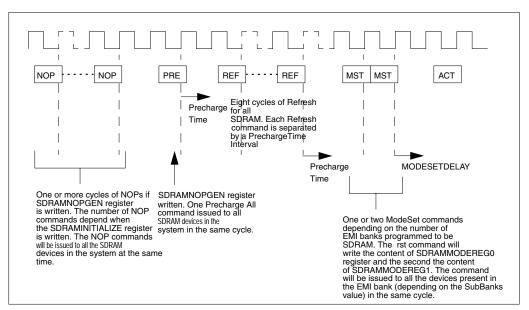

# 1.3.4 Initializing SDRAM devices

An initialization sequence to an SDRAM device must be done after power-on reset by the driver software. The operating system boot-up code or driver software to initialize SDRAM should not read or write SDRAM before completion of the initialization.

# Single data rate SDRAM

- 1 VDD and VDDQ are applied simultaneously on power-up by the system to meet the SDRAM specification.

- 2 CKE is initially low after a power-on reset. With the CKE enable command, write to the LMI.SCR register and all CKE becomes high.

- 3 A minimum pause of 200  $\mu s$  (some of SDRAM only require 100  $\mu s$ ) needs to be provided after powers are stable.

- 4 A precharge all (PALL) is issued to SDRAM.

- 5 Eight autorefresh commands, that is CAS-before-RAS (CBR) cycles send to SDRAM.

- 77 -

21

STMicroelectronics

- 6 A mode register set (MRS) command is issued to program the SDRAM parameters, for example burst length, and CAS\_ Latency.

- 7 A legal command for normal operation can be started after an SDRAM-specific AC timing.

- 8 From reset to the completion of mode register set, the LMI should not drive DQ to avoid contention of drivers. At the same time DQM should keep high.

Mode register set and 8 CBR can be transposed. The minimum pause time might vary from the generation and the vendor of SDRAM. This LMI should be able to support both 100  $\mu s$  or 200  $\mu s$  providing the pause period by software allows this.

# **Double data rate SDRAM**

- 1 The system provides four power in certain sequence. VDD first, VDDQ next then VREF and VTT. VTT is not provided to the LMI, it is externally connected to DQ, DQS and other pins through a series of termination registers. This is required to prevent latch-up in SDRAM devices. LMI should be able to support this power-up sequence. During and after power-on reset, CKE must be kept low.

- 2 After all power supply and reference voltages are stable, and the clock is stable a 200  $\mu s$  pause is necessary.

- 3 CKE should be brought high with the DESELECT command. After this point, unless LMI sends some command, LMI has to send the DESELECT command.

- 4 A precharge all (PALL) is issued to SDRAM.

- 5 A mode register set (MRS) command is issued to program the extended mode register to enable the DLL.

- 6 The MRS command is issued to program the mode register, reset the DLL in SDRAM and program the operating parameters, for example burst length and CAS\_LATENCY.

- 7 Wait ten cycles after the DLL reset and send two CBR commands to SDRAM.

- 8 A MRS command is issued to de-assert DLL initialization bit in the mode register. Other programing parameters should be the same as in previous programing. For some memory vendors, this step can be skipped because they support auto cleaning of the DLL initialization bit.

- 9 After 200 cycles from DLL reset, external memory becomes accessible.

- 57

The LMI's SDRAM controller provides two mechanisms for accomplishing the initialization sequence.

1 NOP, PALL, CKEH and CBR

The SCR register's SMS (SDRAM mode select) field is written with appropriate values to prompt the SDRAM controller to start issuing to start issuing one of these commands. For instance, when SCR.SMS = 3'b100, it results in a single CBR cycle on the SDRAM interface. When SMS = 3'b011, it results in the CKE signals going high. See *Section 1.4.3: SDRAM control register (LMI.SCR) on page 40* for details.

2 Setting the SDRAM device's mode register.Mode Register

The SDRAM's mode register needs to be initialized before actual operation. The software (boot code) initiates a write cycle to the MIM register, and then a write to the SDMR[N] register in the control block. The SDRAM controller then issues an MRS command to all SDRAM devices on row (row [n]).

# Example: issuing MRS command to row 0

Software does a dummy write to SDMR0, the physical address must be arranged in the following way:

- A[31:20]: 1111 1111 1000r,

- A[16:3] contains the value to be written to the SDRAM's mode register,

- data [63:0] is ignored since SDMR0 is a write-only virtual register,

- A[12:3] is copied to MA[9:0], A[18:15] to MA[13:10] and A [14:13] to BA[1:0] when an MRS command is issued to the SDRAM devices.

Software needs to ensure that the SDRAM timing specification (between the MRS command and the first operational command) is met. one way to ensure this is to perform several SDRAM control register reads.

Subsequently, SCR.SMS is written with 3'b000, the normal SDRAM operation can then be started.

Note: Software must program the LMI's MIM register before writing to SDMR[N].

# 1.3.5 Operations

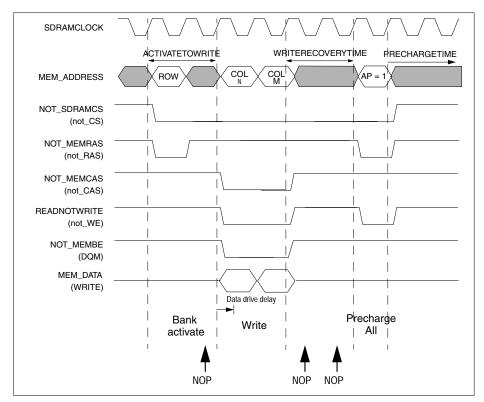

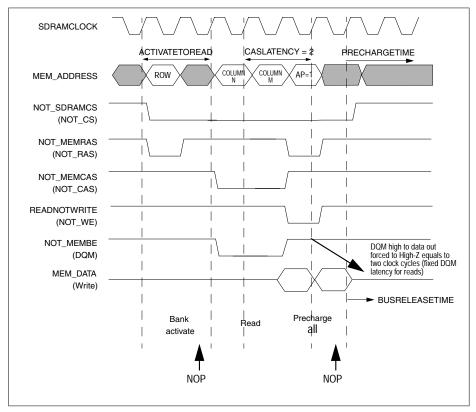

The SDRAM controller supports most PC-SDRAM commands (with the exception of read/write with auto-precharge) and most DDR SDRAM commands. The following truth table lists up all commands supported.

| Function                        | Symbol  | CKE<br>[n - 1] | CKE<br>[n] | NOT<br>_CS | NOT<br>_RAS | NOT<br>_CAS | NOT<br>_WE | MA11 | AP <sup>A</sup><br>(MA10<br>/MA8) | BA<br>[1:0] | MA<br>[9:0] |

|---------------------------------|---------|----------------|------------|------------|-------------|-------------|------------|------|-----------------------------------|-------------|-------------|

| Device deselect                 | DSEL    | Н              | Х          | Н          | Х           | Х           | Х          | Х    | Х                                 | Х           | Х           |

| No operation                    | NOP     | Н              | Х          | L          | Н           | Н           | Н          | Х    | Х                                 | Х           | Х           |

| Burst stop in read              | BST     | Н              | Х          | L          | Н           | Н           | L          | Х    | х                                 | Х           | Х           |

| Read                            | READ    | Н              | Х          | L          | Н           | L           | Н          | V    | L                                 | V           | V           |

| Write                           | WRITE   | Н              | Х          | L          | Н           | L           | L          | V    | L                                 | V           | V           |

| Bank activate                   | ACT     | Н              | Х          | L          | L           | Н           | н          | V    | V                                 | V           | V           |

| Precharge select bank           | PRE     | Н              | Х          | L          | L           | Н           | L          | V    | L                                 | V           | x           |

| Precharge all banks             | PALL    | Н              | х          | L          | L           | Н           | L          | X    | Н                                 | x           | x           |

| Auto refresh                    | CBR     | Н              | Н          | L          | L           | L           | н          | х    | x                                 | х           | Х           |

| Self refresh entry<br>from idle | SLFRSH  | Н              | L          | L          | L           | L           | Н          | x    | Х                                 | x           | х           |

| Self refresh exit               | SLFRSHX | L              | Н          | Н          | Х           | Х           | х          | х    | х                                 | Х           | Х           |

| Power-down<br>entry from idle   | PWRDN   | Н              | L          | Х          | Х           | Х           | х          | x    | Х                                 | x           | X           |

| Power-down exit                 | PWRDNX  | L              | Н          | н          | Х           | Х           | х          | х    | Х                                 | х           | х           |

| Mode register set               | MRS     | Н              | Х          | L          | L           | L           | L          | V    | V                                 | V           | V           |

#### Table 9: SDRAM command truth table

A. AP pin: LMI uses MIM.BY32AP bit to determine if MA8 pin is used to indicate PRE and PALL commands.

*Note:* The LMI does not support full-page burst operation. The LMI issues a BST command to terminate the burst read-only in DDR SDRAM mode.

The timing for issuing these commands is governed by the SDRAM timing register, see *Section 1.4.4: SDRAM timing register (LMI.STR) on page 43* for details. The LMI's SDRAM controller can open up to four pages for each SDRAM row and fully exploit the multi-bank architecture of modern SDRAM devices by tightly pipelining SDRAM commands. The LMI is capable of detecting multiple consecutive requests to the same SDRAM page. The SDRAM controller may combine same-page requests into a single same-page access, providing that the timing of the requests is suitable.

# **Multi-bank ping-pong transaction**

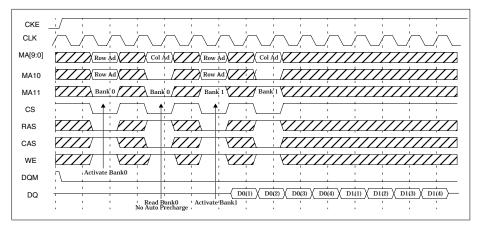

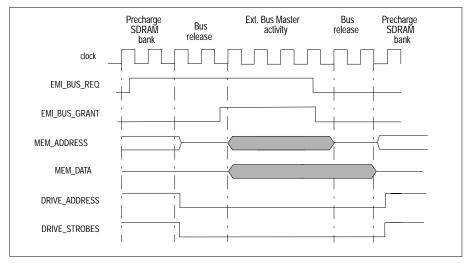

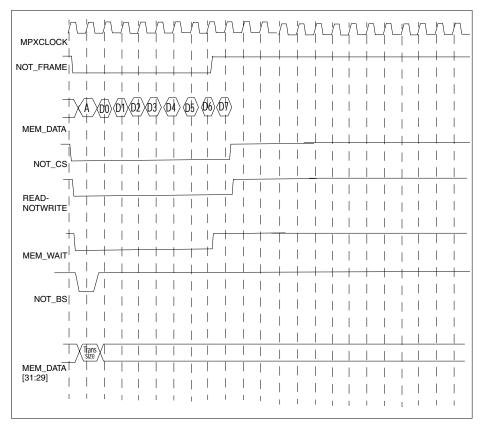

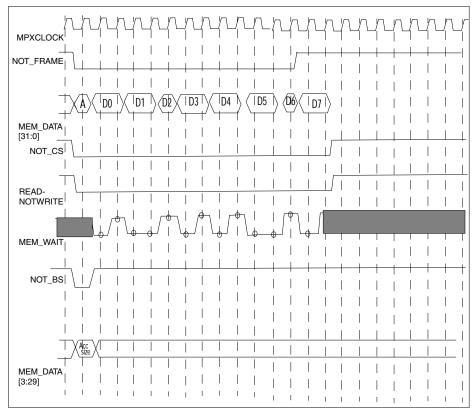

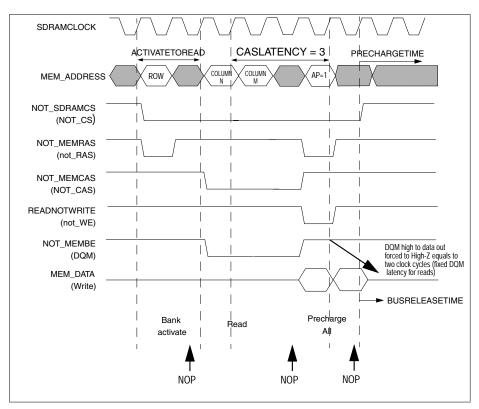

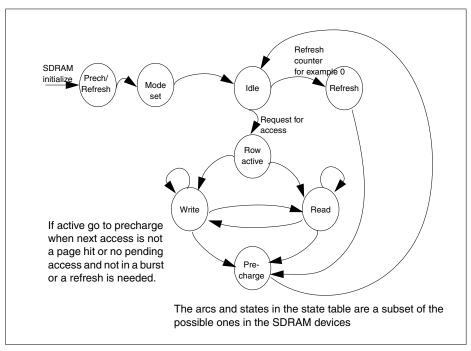

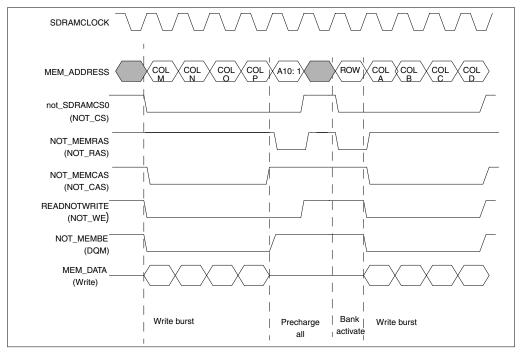

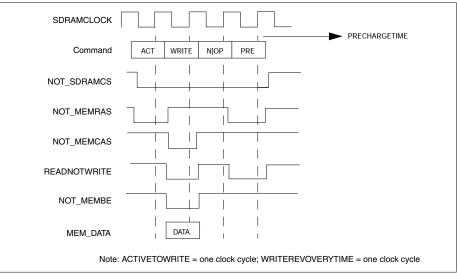

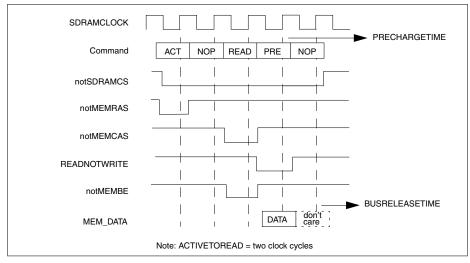

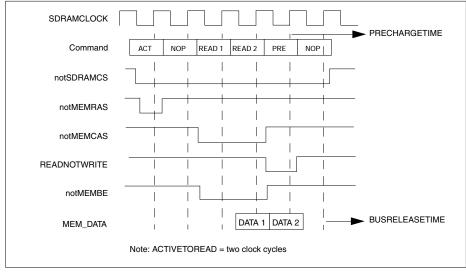

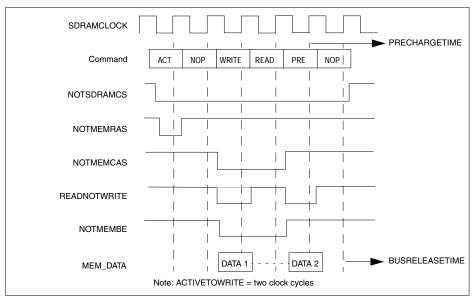

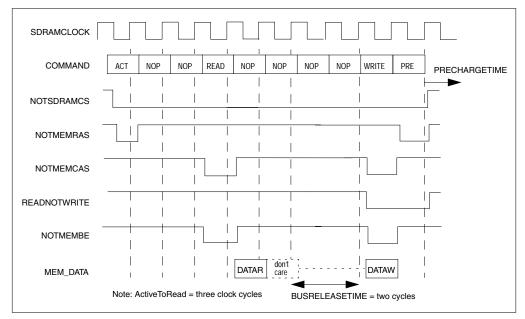

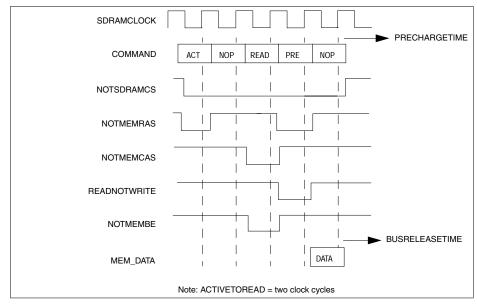

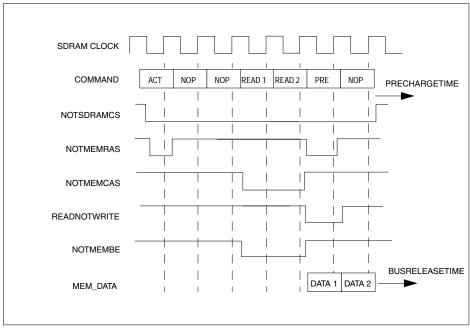

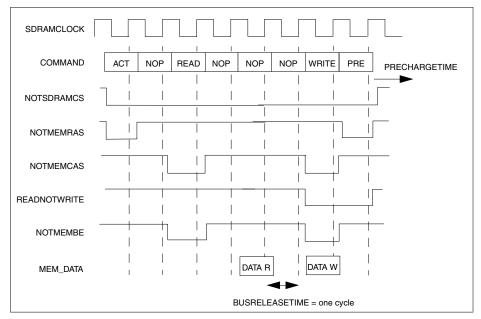

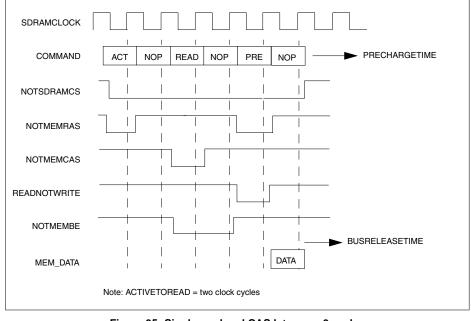

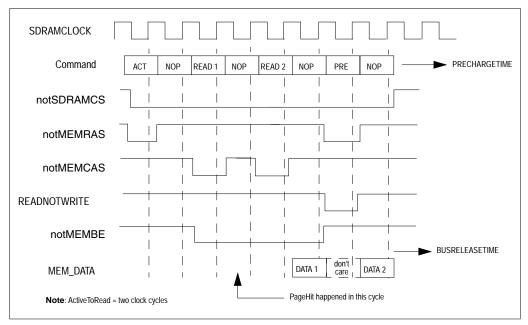

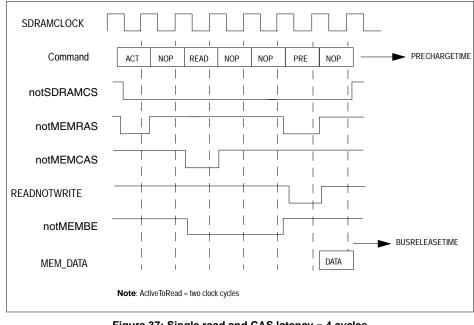

Two bank ping-pong access is illustrated in the following diagram. The peak bandwidth is obtained in this scenario.

Figure 2: PC SDRAM two bank ping pong read

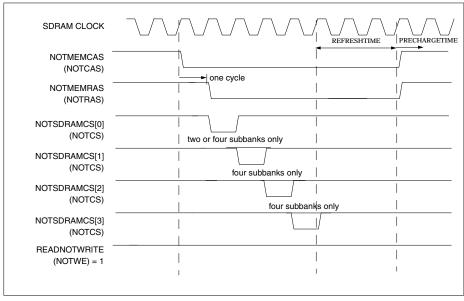

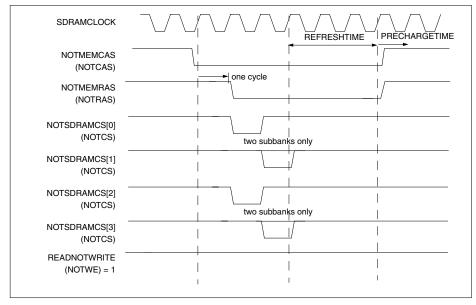

# 1.3.6 Refresh

When DRAM refresh enable is 1 (MIM.DRE = 1), The LMI can automatically generate refresh cycles. A 12-bit quantity (MIM.DRI, DRAM refresh interval) specifies the number of memory clock cycles between refreshes. Software should program MIM.DRI in the inclusive range [128:4095]. The behavior of the DRAM controller is undefined if the LMI is enabled and if DRI is less than 128.

At the start of a refresh interval, the SDRAM controller loads DRI's 12-bit value into an internal counter. This counter is decremented by 1 in each memory clock cycle.

- 77 -

25

STMicroelectronics

When the counter reaches 0, DRI's value is reloaded into the counter and the next refresh interval is started.

All banks must be closed before refresh operation can be performed. The SDRAM controller issues a PRECHARGE ALL (PALL) command if there are any open pages. The SDRAM controller then issues an AUTO REFRESH command (CBR) after the TRP parameter is satisfied. The next row ACT command can be issued Trc clock (LMI.STR.SRC) later.

The SDRAM controller performs exactly one refresh operation for each refresh interval. It attempts to perform CBR as soon as possible within the refresh interval. When the counter  $\leq$  128 and CBR is not issued in the current refresh interval the SDRAM controller causes any current SDRAM access to complete in a timely manner by ensuring that the detection of same-page SDRAM access is prevented. Subsequently it performs PALL and CBR commands.

The maximum refresh rate that the LMI can support is one row every 128 clock cycles. At this rate, however, the detection of same-page SDRAM accesses will be permanently disabled.

As an example, the hard reset value of DRI is 1,562. For 100 MHz MCLKO, then this allows 1,024 refreshes in less than 16 ms.

*Note:* On average, the interval between two refreshes is determined by the DRI setting. However the interval between any two successive refreshes could be larger or smaller than DRI by (a page miss 32-byte transfer) clocks.

### **1.3.7 Power management**

The LMI provides one power management mechanism.

When the LMI receives STBY\_REQ from the power-down management unit (PMU), the LMI prepares the SDRAM rows to enter low power state. The sequence of events for both entering and leaving standby mode is described below. To make the correct sequence, cooperation with the software driver is important.

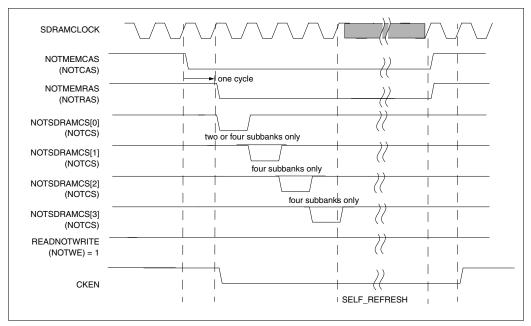

# **Entering standby**

- 1 At first, no initiators should be issuing transaction requests to the LMI.

- 2 The standby management program should issue CBR command as the last command to LMI.

- 3 The standby management program asserts STBY\_REQ to LMI.

- 4 All outstanding transaction requests are serviced.

- 5 The SDRAM controller issues a self refresh command and lowers CKE[1:0] to both SDRAM rows. The SDRAM autonomously refreshes itself for the duration of the power-down mode.

- 6 LMI asserts STBY\_ACK to PMU. The clock (MCLKO) can now be stopped.

# Leaving standby by causes other than power-on reset

- 1 PMU resumes the LMI's SuperHyway clock and SDRAM clock and deasserts STBY\_REQ.

- 2 The LMI de-asserts STBY\_ACK, and starts to count down from (256 x SCR.CST) to zero every MCLK cycle.

- 3 When count down reaches zero, the SDRAM controller asserts all CKE[1:0] pins and sends **deselect** commands continuously. All SDRAM rows exit from self-refresh mode.

- 4 The first valid command can be issued ten cycles after CKE's rising edge.

- 5 In the case of DDR SDRAM, the LMI issues numbers of CBR commands defined by the CSR.BRFSH field.

# 1.3.8 Caution when programming SDRAM's mode register

To effectively support SuperHyway Load32 and Store32 packets, the LMI's SDRAM controller uses MIM.DT (SDRAM type) and MIM.BW (external data bus width) to determine the burst length.

| MIM.DT device type | MIM.BW bus width | Burst length |

|--------------------|------------------|--------------|

| 0: PC SDRAM        | 00: 16-bit       | 8            |

|                    | 01: 32-bit       | 8            |

|                    | 10: 64-bit       | 4            |

| 1: DDR SDRAM       | 00: 16-bit       | 8            |

|                    | 01: 32-bit       | 8            |

|                    | 10: 64-bit       | 4            |

Table 10: Determining burst length for Load32 and Store32 packets

For a 16-bit external data bus width (for either PC-SDRAM or DDR SDRAM), the LMI splits a SuperHyway Load32 or Store32 packet into multiple SDRAM transactions, with a burst of eight for each transaction. Therefore the BL field of the SDRAM device's mode register must be programmed to match the LMI's burst length behavior in the third column.

# 1.3.9 Using registered DIMM

When using registered DIMM, the MIM register's DIMM bit needs to be set to 1, so that LMI can:

- delay data output by one cycle to synchronize with the buffered (on DIMM card) command signals before they reach the SDRAM devices during a write operation,

- add one MCLK cycle to the setting of STR.SCL bit (CAS Latency). STR.SCL bits should be programmed with the same CL latency as the CL setting in the SDRAM device's mode register.

- 57 -

### 1.3.10 Others